## **C-DIAS DMS Module**

**CAI 025**

For two resistance bridges 2mV/V, 20mV/V

For each connector, a measurement bridge can be connected with a 4-wire cable in 2mV/V or 20mV/V resolution. The supply voltage for the bridge is 5V. The minimum resistance is  $100\Omega$  per bridge.

### **Technical Data**

### Input specifications

| Number of channels              | 2 (4-wire connection)              |                   |

|---------------------------------|------------------------------------|-------------------|

| Measurement range               | 2mV/V or 20mV/V                    |                   |

| Measurement value               | 0 – 16000                          |                   |

| Resolution                      | 14-bit                             |                   |

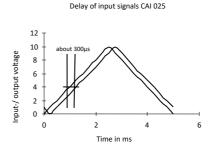

| Conversion time per channel     | ≤1ms                               |                   |

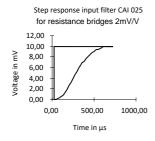

| Input filter                    | Cutoff frequency 1kHz (1ms)        | Low pass 3 system |

| Supply voltage                  | 5V / ±2,5%                         |                   |

| Maximum voltage supply capacity | 100mA maximum, short circuit proof |                   |

| Analog measurement precision    | ±0,3% of maximum Measurement value |                   |

| Repeating accuracy              | 2mV/V<br>±0,3%                     | 20mV/V<br>±0,2%   |

| Linearity error                 | 2mV/V<br>±0,6%                     | 20mV/V<br>±0,2%   |

20.11.2023 Page 1

## **Electrical requirements**

| Power supply from C-DIAS bus                    | 5V / +24V       |               |

|-------------------------------------------------|-----------------|---------------|

| Current consumption of C-DIAS bus (+5V supply)  | Typically 75mA  | Maximum 100mA |

| Current consumption of C-DIAS bus (+24V supply) | Typically 140mA | Maximum 210mA |

#### Miscellaneous

| Article number   | 12-009-025   |  |

|------------------|--------------|--|

| Hardware version | 1.x          |  |

| Standardization  | UL (E247993) |  |

#### **Environmental conditions**

| Storage temperature   | -20 – +85°C                                      |         |  |

|-----------------------|--------------------------------------------------|---------|--|

| Operating temperature | 0 - +60°C                                        |         |  |

| Humidity              | 0 – 95%, uncondensed                             |         |  |

| EMV stability         | According to EN 61000-6-2:2001 (industrial area) |         |  |

| Shock resistance      | EN 60068-2-27                                    | 150m/s² |  |

| Protection            | EN 60529                                         | IP 20   |  |

Page 2a 20.11.2023

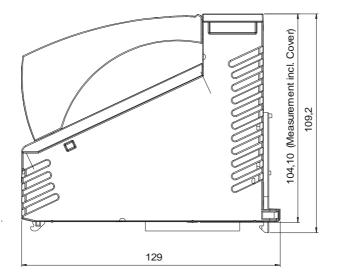

# **Mechanical Dimensions**

20.11.2023 Page 3

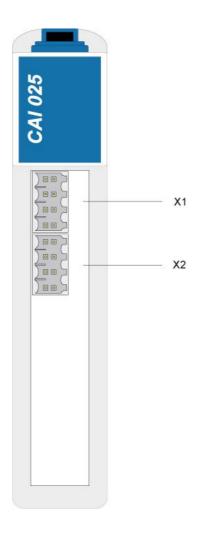

# **Connector Layout**

Page 4 20.11.2023

#### X1:

| Pin | Assignment         |  |

|-----|--------------------|--|

| 1   | Bridge input 1-    |  |

| 2   | Bridge input 1+    |  |

| 3   | AGND               |  |

| 4   | +5V supply voltage |  |

| 5   | Bridge input 1-    |  |

| 6   | Bridge input 1+    |  |

| 7   | AGND               |  |

| 8   | +5V supply voltage |  |

Bridge 2 mV/V

Bridge 20 mV/V

#### X2:

| Pin | Assignment         |

|-----|--------------------|

| 1   | Bridge input 2-    |

| 2   | Bridge input 2+    |

| 3   | AGND               |

| 4   | +5V supply voltage |

| 5   | Bridge input 2-    |

| 6   | Bridge input 2+    |

| 7   | AGND               |

| 8   | +5V supply voltage |

Bridge 2 mV/V

Bridge 20 mV/V

Only one connector per measurement bridge is allowed. The minimum resistance per bridge is  $100\Omega$ .

### **Applicable connectors**

X1, X2: 8-pin. Weidmüller plug B2L/B2CF 3,5/8

The complete C-DIAS CKL 046 connector set with spring terminals is available from Sigmatek under the article number 12-600-046.

20.11.2023 Page 5b

## **Wiring Guidelines**

The signals recorded by the analog modules are very small, as compared to the digital signals. To ensure error-free operation, a careful wiring method must be followed:

- The DIN rail must have an adequate mass connection.

- The connection lines to the source of the analog signals must be as short as possible and parallel wiring to digital signal lines must be avoided.

- The signal lines must be shielded.

- The shielding should be connected to a shielding bus. If no shielding bus is available, the shield can also be clamped to the connectors (see below).

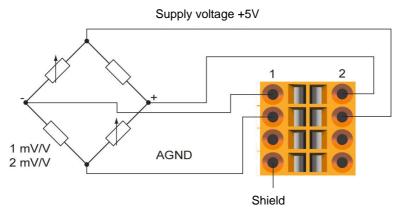

#### With 2mV/V Measurement Bridge Circuit

Connection diagram 1

Page 6a 20.11.2023

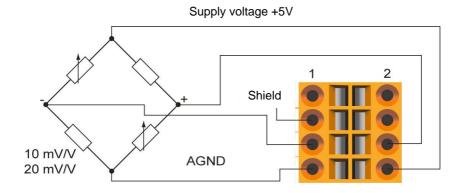

# With 20mV/V Measurement Bridge Circuit

Connection diagram 2

20.11.2023 Page 7 a

# Addressing

| Address | RD/WR   | Function / Bits                                                       |  |

|---------|---------|-----------------------------------------------------------------------|--|

| \$00    | RD16    | 14-bit reference voltage for the analog measurement value             |  |

| \$02    | RD16    | Analog measurement value, Channel 1; 14-bit                           |  |

| \$04    | RD16    | Analog measurement value, Channel 2; 14-bit                           |  |

| \$06    | RD16    | Analog measurement value, Channel 3; 14-bit                           |  |

| \$08    | RD16    | Analog measurement value, Channel 4; 14-bit                           |  |

|         |         |                                                                       |  |

| \$16    | WR8     | ADC-DAC configuration: Bit 7 Enable 10 V reference                    |  |

|         |         |                                                                       |  |

| \$16    | RD8     | ADC-DAC Status: Bit 0 10 V reference OK                               |  |

| , -     |         | Bit 7 10 V reference enabled                                          |  |

| \$18    | RD8     | PLL status register Bit 1 = PLL online Bit 0 = PLL lock (PLL latched) |  |

| \$19    | RD8/WR8 | PLL configuration register Bit 03: Period of the PLL base time in ms  |  |

|         |         |                                                                       |  |

| \$1A    | RD8     | Reserved                                                              |  |

|         |         |                                                                       |  |

| \$1B    | RD8     | Xilinx Version                                                        |  |

|         |         |                                                                       |  |

Page 8 20.11.2023

# Calibration data (the serial EEPROM is organized by bite)

| Address   | DATA   | Description                                               |

|-----------|--------|-----------------------------------------------------------|

| \$00      | \$xx   | Check sum                                                 |

| \$01      | 123    | Identification                                            |

| \$02      | 5      | Module group 5 = CAI                                      |

| \$03      | 15     | Module version                                            |

| \$04      | 4      | Number of channels                                        |

| \$05      | 10     | Hardware version \$10 = HW 1.0                            |

| \$06-\$3F | 0      | FILL                                                      |

| \$10      |        | Serial number                                             |

|           |        |                                                           |

|           |        | Al calibration data 0 – 10Vref                            |

| \$40      | \$xxxx | Check sum                                                 |

| \$42      | 12345  | Identification                                            |

| \$44      | 16     | Length of the following data blocks in WORD               |

| \$46      | 4      | Number of channels                                        |

| \$48      |        | Al0 Offset = Reference voltage at the time of calibration |

| \$4A      |        | Al0 Multiplicand is not used                              |

| \$4C      |        | Al0 Divisor is not used                                   |

| \$4E      |        | Al1 Offset                                                |

| \$50      |        | Al1 Multiplicand                                          |

| \$52      |        | Al1 Divisor                                               |

| \$54      |        | Al2 Offset                                                |

| \$56      |        | Al2 Multiplicand                                          |

| \$58      |        | Al2 Divisor                                               |

| \$5A      |        | Al3 Offset                                                |

| \$5C      |        | Al3 Multiplicand                                          |

| \$5E      |        | Al3 Divisor                                               |

| \$60      |        | Al4 Offset                                                |

| \$62      |        | Al4 Multiplicand                                          |

| \$64      |        | Al4 Divisor                                               |

| \$66-\$FF | 0      | FILL                                                      |

20.11.2023 Page 9a

Page 10 20.11.2023