## **VARAN Client Board**

## VEB 011/012

Versatile Automation Random Access Network

This client board provides a simple method of connecting any periphery modules to the VARAN bus.

## **Technical Data**

#### **Performance Data**

| Internal memory                     | Serial 4-MBit-Flash                                                                                     |

|-------------------------------------|---------------------------------------------------------------------------------------------------------|

| Interfacing                         | 1 x VARAN (Client) (maximum length: 100 m)<br>1 x Periphery interface                                   |

| Connection to periphery mod-<br>ule | Over 50-pin. Board-to-Board- connector plug, 0,8 mm spacing<br>(Type ERNI Microstac, order no.: 114713) |

#### **Electrical Requirements**

| Internal supply voltage (VDD)             | Typically +3,3 V DC (±4 %)<br>(Supplied by the periphery module over the 50-pin connector plug) |

|-------------------------------------------|-------------------------------------------------------------------------------------------------|

| Current consumption of the voltage supply | Minimum 250 mA<br>(Depending on the external circuit)                                           |

#### **Miscellaneous**

|                  | VEB 011    | VEB 012    |

|------------------|------------|------------|

| Article number   | 16-081-011 | 16-081-012 |

| Hardware version | 1.x        | 1.x        |

#### **Environmental Conditions**

| Storage temperature                 | -20 – +85 °C                       |           |  |  |

|-------------------------------------|------------------------------------|-----------|--|--|

| Operating temperature <sup>1)</sup> | VEB 011                            | VEB 012   |  |  |

|                                     | 0 – 70 °C                          | 0 – 85 °C |  |  |

|                                     | VEB 011/012                        |           |  |  |

| Humidity                            | 0 – 95 %, uncondensed              |           |  |  |

| EMV stability                       | 2)                                 |           |  |  |

| Shock resistance                    | EN 60068-2-27 150 m/s <sup>2</sup> |           |  |  |

<sup>&</sup>lt;sup>1)</sup> The operating temperature of the entire unit must be defined individually for each application since the operating conditions (mounting position, housing, and heat source in the vicinity of the module) are not known. <sup>2)</sup> The EMV stability has to be tested separately in the complete system for each application.

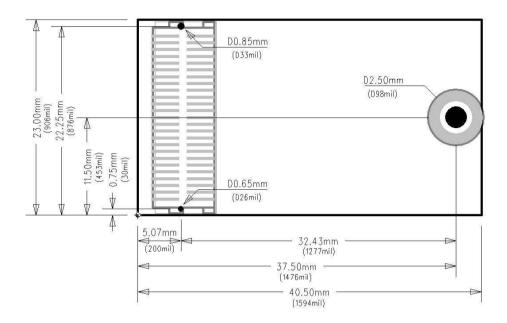

## **Mechanical Dimensions**

The dimensioning of the center holes of the 50-pole ERNI Board-to-Board connector is effective for the plugs on the base board (doesn't show the position of the connectors on the VEB).

The VEB is shown from the connector back side in this illustration.

The height of the component parts on the base board under the VEB must not exceed 3 mm.

## **Connector Layout**

| 12  | Pin      | Xilinx<br>Identifier | Bus Mode            |          | DPRAM Mod           | e        | IO Mode          |           |

|-----|----------|----------------------|---------------------|----------|---------------------|----------|------------------|-----------|

|     | 1        |                      | GND                 |          | GND                 |          | GND              |           |

|     | 2        |                      | GND                 |          | GND                 |          | GND              |           |

|     | 3        | V2                   | D0                  | IO       | D0                  | IO       | IN9              | IN        |

|     | 4        | V1                   | -                   |          | -                   |          | OUT9             | OUT       |

|     | 5        | V4                   | D1                  | IO       | D1                  | IO       | IN10             | IN        |

| = = | 6        | V3                   | -                   |          | -                   |          | OUT10            | OUT       |

|     | 7        | V6                   | D2                  | IO       | D2                  | IO       | IN11             | IN        |

|     | 8        | V5                   | -                   |          | -                   |          | OUT11            | OUT       |

|     | 9        | V8                   | D3                  | 10       | D3                  | 10       | IN12             | IN        |

|     | 10       | V7                   | -                   |          | -                   |          | OUT12            | OUT       |

|     | 11       | V10                  | D4                  | 10       | D4                  | 10       | IN13             | IN        |

|     | 12       | V9                   | -                   | 10       | -                   | 10       | OUT13            | OUT       |

|     | 13       | V12                  | D5                  | IO       | D5                  | IO       | IN14             | IN        |

|     | 14       | V11                  | Mode0               | IN<br>IO | Mode0               | IN       | Mode0            | IN        |

|     | 15       | V14                  | D6<br>Mada1         | IN       | D6<br>Mada1         | IO<br>IN | IN15             | IN<br>IN  |

|     | 16<br>17 | V13                  | Mode1<br>D7         | IN       | Mode1<br>D7         | IN       | Mode1            | IN        |

|     | 17       | V16<br>V15           | Mode2               | IN       | Mode2               | IN       | IN16<br>Mode2    | IN        |

|     | 10       | V15                  | VDD                 | IIN      | VDD                 | IIN      | VDD              | IIN       |

|     | 20       |                      | VDD                 |          | VDD                 |          | VDD              |           |

|     | 20       |                      | GND                 |          | GND                 |          | GND              |           |

|     | 22       | V17                  | Ready               | IN       | -                   |          | -                |           |

|     | 23       | VII                  | Phy_RX+             |          | Phy_RX+             |          | Phy_RX+          |           |

|     | 24       | V18                  | Sync                | OUT      | Sync                | OUT      |                  |           |

|     | 25       | 10                   | Phy_RX-             |          | Phy_RX-             |          | Phy_RX-          |           |

|     | 26       | V19                  | A0                  | OUT      | A0                  | OUT      | IN1              | IN        |

|     | 27       | -                    | Phy_TX+             |          | Phy_TX+             |          | Phy_TX+          |           |

|     | 28       | V20                  | A1                  | OUT      | A1                  | OUT      | IN2              | IN        |

|     | 29       |                      | Phy_TX-             |          | Phy_TX-             |          | Phy_TX-          |           |

|     | 30       | V21                  | A2                  | OUT      | A2                  | OUT      | IN3              | IN        |

|     | 31       |                      | VB +3V3             |          | VB +3V3             |          | VB +3V3          |           |

|     | 32       | V22                  | A3                  | OUT      | A3                  | OUT      | IN4              | IN        |

|     | 33       | V24                  | CLK 25 MHz          | OUT      | CLK 25 MHz          | OUT      | CLK 25 MHz       | OUT       |

|     | 34       | V23                  | A4                  | OUT      | A4                  | OUT      | IN5              | IN        |

|     | 35       | V26                  | /Periphery Reset    | OUT      | /Periphery Reset    | OUT      | /Periphery Reset | OUT       |

|     | 36       | V25                  | A5                  | OUT      | A5                  | OUT      | IN6              | IN        |

|     | 37       | V28                  | -                   | 0.UT     | -                   | 0. IT    | -                |           |

|     | 38       | V27                  | A6                  | OUT      | A6                  | OUT      | IN7              | IN        |

|     | 39       | V30                  | R/W                 | OUT      | R/W                 | OUT      | OUT8             | OUT       |

|     | 40       | V29                  | A7                  | OUT      | A7                  | OUT      | IN8              | IN<br>OUT |

|     | 41<br>42 | V32<br>V31           | -<br>A8             | OUT      | -<br>A8             | OUT      | OUT6<br>OUT7     | OUT       |

|     | 42       | V31                  |                     | 001      | -                   | 001      | /Phy_led_link    | 001       |

|     | 43       | V33                  | /Phy_led_link<br>A9 | OUT      | /Phy_led_link<br>A9 | OUT      | OUT5             | OUT       |

|     | 44<br>45 | V33                  | /Phy_led_active     | 001      | /Phy_led_active     | 001      | /Phy_led_active  | 001       |

|     | 45       | V34                  | A10                 | OUT      | A10                 | OUT      | OUT4             | OUT       |

|     | 40       | V34<br>V36           | /CS Hex Switch      | 001      | /CS Hex Switch      | 001      | OUT2             | OUT       |

|     | 48       | V35                  | A11                 | OUT      | A11                 | OUT      | OUT3             | OUT       |

|     | 40       | 100                  | GND                 | 001      | GND                 | 001      | GND              | 001       |

|     | 50       | V37                  | /CS                 | OUT      | /CS                 | OUT      | OUT1             | OUT       |

|     | 50       | v3/                  | /03                 | 001      | 100                 | 001      | 0011             |           |

VEB 011/012

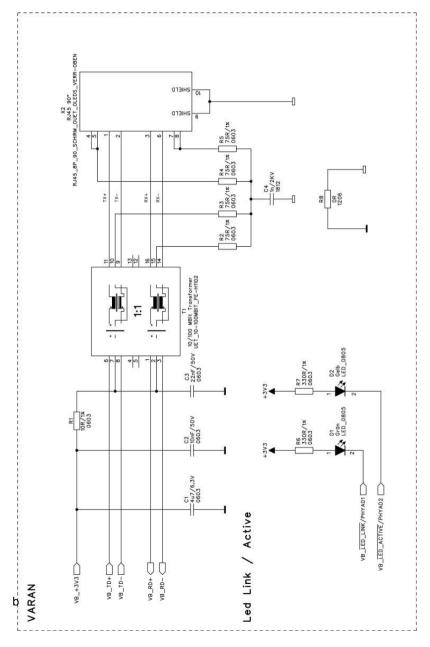

## Electrical bonding

## Layout guidelines

- Place blocking capacitors with 100 nF to the supply pins (+3V3) of the Board-to-Board connectors.

- The distance between the transformer (Pulse H1102NLT) and the RJ45 plug connector has to be kept to a minimum (<25 mm)</p>

- The distance between the transformer and the 50-pole VEB plug should not exceed 50mm, if possible.

- The VARAN differential lines TD+/TD- and RD+/RD- are

- as short as possible

- parallel

- of same length

- ... to route

- > Furthermore differential lines should have the following properties:

- Distance between two differential line pairs >0,38 mm

- Distance of the differential lines to the circuit board angles >25 mm

- Distance of the differential lines to other signals >0,76 mm

- Continuous GND area under the differential lines

- Do not cross differential lines with other signals

- Do not route differential lines under components

## **Mode Register**

The mode pins (v11, v13, v15) are latched in the FPGA and the selected mode can be read out from the register. Following modes are defined:

| V15 | V13 | V11 | Mode             |

|-----|-----|-----|------------------|

| 0   | 0   | 0   | "000" Bus Mode   |

| 0   | 0   | 1   | "001" IO Mode    |

| 0   | 1   | 0   | "010" DPRAM Mode |

## **Bus Mode**

In the Bus mode the VEB 011 is the bus master. The Sync signal is the output of the PLL (sync out 0) – see VARAN Bus specification. This signal can be used for synchronisation of the periphery.

| Name  | Description      | Port  | Pins (0 to)                                     |

|-------|------------------|-------|-------------------------------------------------|

| А     | Address (12 bit) | out   | V19, 20, 21, 22, 23, 25, 27, 29, 31, 33, 34, 35 |

| D     | Data (8 bit)     | inout | V2, 4, 6, 8, 10, 12, 14, 16                     |

| R/W   | Read/Write       | out   | V30                                             |

| CS    | Chip select      | out   | V37                                             |

| Sync  | Sync             | out   | V18                                             |

| Ready | Ready            | in    | V17                                             |

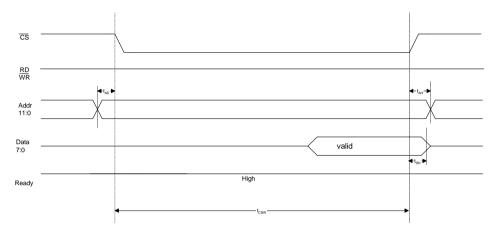

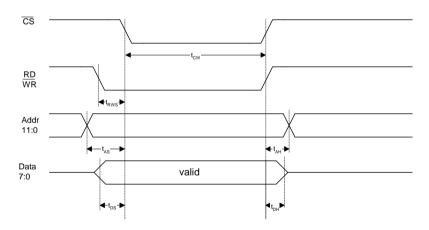

## **Timing Diagram**

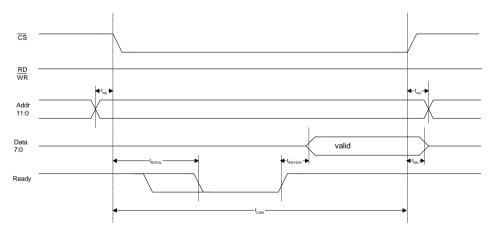

#### Read (without wait states)

#### Read (with wait states)

#### VEB 011/012

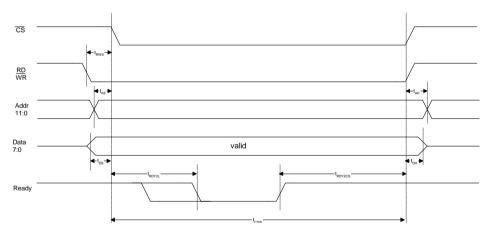

#### Write (without wait states)

#### Write (with wait states)

| Timing                                  | Time (ns) |      | Description                   |

|-----------------------------------------|-----------|------|-------------------------------|

| ' i i i i i i i i i i i i i i i i i i i | min.      | max. | Description                   |

| t <sub>CSW</sub>                        | 220       | -    | Chip select low width         |

| t <sub>RWS</sub>                        | 5         | -    | Read write setup time         |

| t <sub>AS</sub>                         | 5         | -    | Address setup time            |

| t <sub>DS</sub>                         | 5         | -    | Data setup time               |

| t <sub>DH</sub>                         | 0         | -    | Data hold time                |

| t <sub>AH</sub>                         | 5         | -    | Address hold time             |

| t <sub>RDY2L</sub>                      | 120       | -    | Chip select to ready low time |

| t <sub>RDY2DV</sub>                     | -         | 5    | Ready to data valid time      |

| t <sub>RDY2CS</sub>                     | 60        | -    | Ready to chip select          |

#### **Timing Characteristics**

## **DPRAM Mode**

In the DPRAM mode the VEB 011 is the bus client. An external bus master can access the DPRAM in the FPGA. The DPRAM is organized in 4096 x 8 bits on both sides. The Sync signal is the output of the PLL (sync out 0) – see VARAN Bus specification. This signal can be used for synchronisation of the periphery.

| Name | Description      | Port  | Pins (0 to)                                     |

|------|------------------|-------|-------------------------------------------------|

| A    | Address (12 bit) | in    | V19, 20, 21, 22, 23, 25, 27, 29, 31, 33, 34, 35 |

| D    | Data (8 bit)     | inout | V2, 4, 6, 8, 10, 12, 14, 16                     |

| R/W  | Read/Write       | in    | V30                                             |

| CS   | Chip select      | in    | V37                                             |

| Sync | Sync             | out   | V18                                             |

## **Timing Diagram**

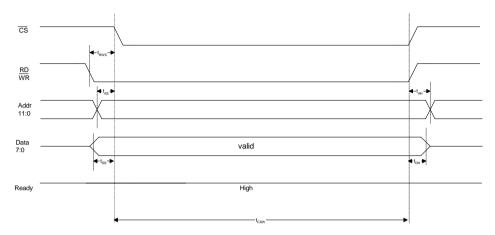

#### Read

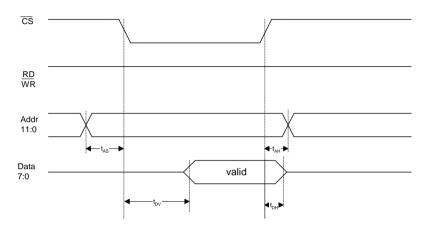

#### Write

#### **Timing Characteristics**

| Timing           | Time (ns) |      | Description                    |

|------------------|-----------|------|--------------------------------|

| rinning          | min.      | max. | Description                    |

| t <sub>cw</sub>  | 55        | -    | Chip select to end of write    |

| t <sub>RWS</sub> | 0         | -    | Read write setup time          |

| t <sub>AS</sub>  | 0         | -    | Address setup time             |

| t <sub>DS</sub>  | 0         | -    | Data setup time                |

| t <sub>DH</sub>  | 0         | -    | Data hold time                 |

| t <sub>AH</sub>  | 0         | -    | Address hold time              |

| t <sub>DV</sub>  | -         | 70   | Chip select to data valid time |

## **Read Hex Switch**

After switch-on the FPGA reads in the hex switches in Bus Mode and DPRAM Mode. During this process the periphery remains in reset.

The read hex switches are stored in the varan configuration register.

| Name       | Description | Port  | Pins (0 to)                 |

|------------|-------------|-------|-----------------------------|

| Hex Switch | Hex Switch  | inout | V2, 4, 6, 8, 10, 12, 14, 16 |

|            | (8 bit)     |       |                             |

| CS         | Chip select | out   | V36                         |

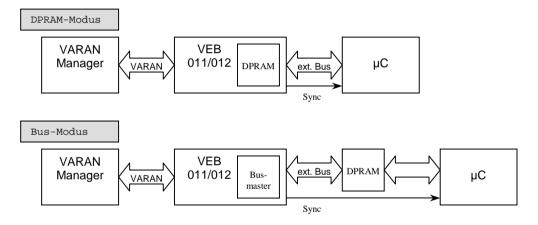

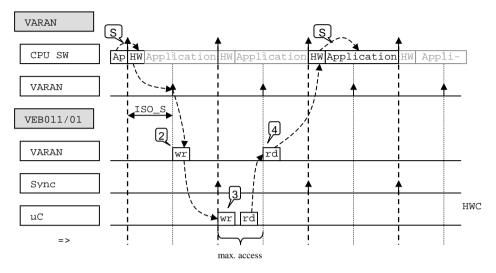

## VEB 011/012 Time response

A DPRAM gives a microcomputer the option of exchanging data with the VARAN system. For this, the VEB 011/012 provides two variations, one that uses the FPGA internal DPRAM and another for an external DPRAM. So that data consistency in the 4-kbyte DPRAM is ensured, the microcomputer must be synchronized with the VARAN bus and can only exchange data in the allowed time window. The Sync signal gives the microcomputer permission to access the DPRAM. The data exchange must then be completed within half the VARAN system time to avoid generating inconsistent data.

#### **Block Diagram**

#### Time diagram

#### Hardware Class

| SW    | => Software                                    |

|-------|------------------------------------------------|

| wr    | => Write                                       |

| rd    | => Read                                        |

| ISO_S | => ISO Start point (adjustable from 10 – 90 %) |

#### Zeitliches Verhalten am VEB011/012

- 1 HW Class writes to DO RAM

- 2 VARAN writes to DPRAM

- 3  $\mu$ C writes and reads DPRAM

- 4 VARAN read from DPRAM

- 5 HW Class reads from DO RAM

500 µs (half Cycle@1ms Cycle time)

500 µs (half Cycle@1ms Cycle time)

VEB 011/012

## Addressing

| Address<br>(hex) | Size (Byte) | Access type | Description                                                                                                                                                                       | Reset value |  |  |

|------------------|-------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|

| Memory           |             |             |                                                                                                                                                                                   |             |  |  |

| 0000             | 528         | -           | Reserved                                                                                                                                                                          |             |  |  |

| 0210             | 1           | r           | VEB011 Mode Register<br>Bit 0 2: Mode<br>Bit 3 7: Reserved<br>"000" Bus mode<br>"001" IO mode<br>"010" DPRAM mode                                                                 | 00          |  |  |

| 0211             | 15          | -           | Reserved                                                                                                                                                                          |             |  |  |

| 0220             | 1           | w           | Digital Out Register<br>Bit 0: OUT1<br>Bit 1: OUT2<br>Bit 2: OUT3<br>Bit 3: OUT4<br>Bit 4: OUT5<br>Bit 5: OUT6<br>Bit 6: OUT7<br>Bit 7: OUT8<br>(Access only allowed in IO mode)  | 00          |  |  |

| 0220             | 1           | r           | Digital Input Register<br>Bit 0: IN1<br>Bit 1: IN2<br>Bit 2: IN3<br>Bit 3: IN4<br>Bit 4: IN5<br>Bit 5: IN6<br>Bit 6: IN7<br>Bit 7: IN8<br>(Access only allowed in IO mode)        |             |  |  |

| 0221             | 1           | w           | Digital Out Register<br>Bit 0: OUT9<br>Bit 1: OUT10<br>Bit 2: OUT11<br>Bit 3: OUT12<br>Bit 4: OUT13<br>Bit 5 7: Reserved<br>(Access only allowed in IO mode)                      | 00          |  |  |

| 0221             | 1           | r           | Digital Input Register<br>Bit 0: IN9<br>Bit 1: IN10<br>Bit 2: IN11<br>Bit 3: IN12<br>Bit 4: IN13<br>Bit 5: IN14<br>Bit 6: IN15<br>Bit 7: IN16<br>(Access only allowed in IO mode) |             |  |  |

#### VARAN CLIENT BOARD

VEB 011/012

| 0222 | 3550 | -   | Reserved                                                                                                                                                                                                                                 |  |

|------|------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1000 | 4096 | r/w | Bus Master (Access only allowed in Bus mode)<br>Note:<br>These registers have a slower processing<br>time of the VARAN client.<br>t <sub>client</sub> = 230 ns + 300 ns/byte<br>(see VARAN Bus timing in the VARAN Bus<br>specification) |  |

| 2000 | 4096 | r/w | DPRAM<br>(Access only allowed in DPRAM mode)                                                                                                                                                                                             |  |

#### More information on the VARAN bus can be found in the VARAN bus specifications!

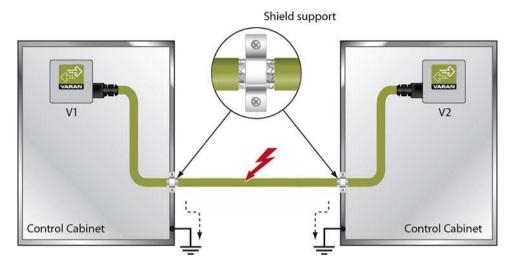

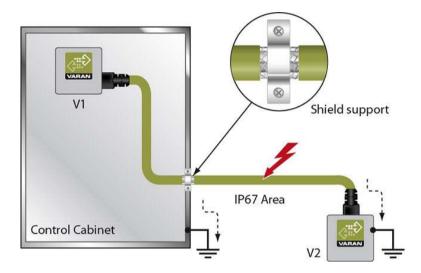

## **VARAN Recommended Shielding**

The VARAN real-time Ethernet bus system offers robust performance in harsh industrial environments. Through the use of IEEE 802.3 standard Ethernet physics, the potential between an Ethernet line and sending/receiving components is kept separate. The VARAN Manager resends messages to a bus participant immediately when an error occurs. It is principally recommended that the shielding guidelines below be followed.

For applications in which the bus line is run outside the control cabinet, correct shielding is required. This is especially important, if due to physical requirements, the bus lines must be placed next to sources of strong electromagnetic noise. It is recommended that whenever possible, to avoid wiring VARAN-Bus lines parallel to power cables.

SIGMATEK recommends the use of **CAT5e** industrial Ethernet bus lines.

For the shielding variants, an S-FTP bus line is recommended, which is a symmetric, multiwire cable with unshielded pairs. For the total shielding, a combination of foil and braiding is used; it is recommended that an unvarnished variant be used.

## The VARAN cable must be secured at a distance of 20 cm from the connector for protection against vibration!

# 1. Wiring from the Control Cabinet to an External VARAN Component

If the Ethernet lines are connected from a VARAN component to a VARAN node outside the control cabinet, the shielding should be placed at the entry point to the control cabinet housing. All noise can then be deflected from the electronic components before reaching the module.

## 2. Wiring Outside of the Control Cabinet

If a VARAN bus cable must be placed outside of the control cabinet only, no additional shield connection is required. This requires that only IP67 modules and connectors be used. These components are very robust and noise resistant. The shielding for all sockets in IP67 modules are internally connected to common bus or electrically connected to the housing, whereby the deflection of voltage spikes does not flow through the electronics.

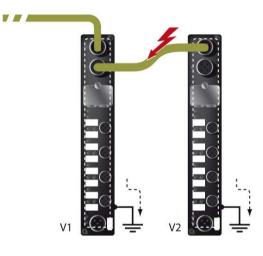

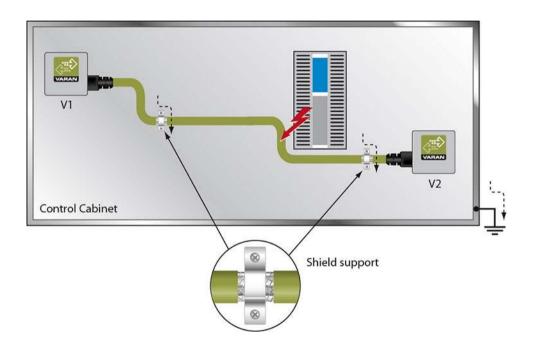

## 3. Shielding for Wiring Within the Control Cabinet

Sources of strong electromagnetic noise located within the control cabinet (drives, Transformers, etc.) can induce interference in a VARAN bus line. Spike voltages are deflected over the metallic housing of a RJ45 connector. Noise is conducted through the control cabinet housing without further action from the electronic components To eliminate sources of noise during data transfer, it is recommended that the shielding from all electronic components be connected within the control cabinet.

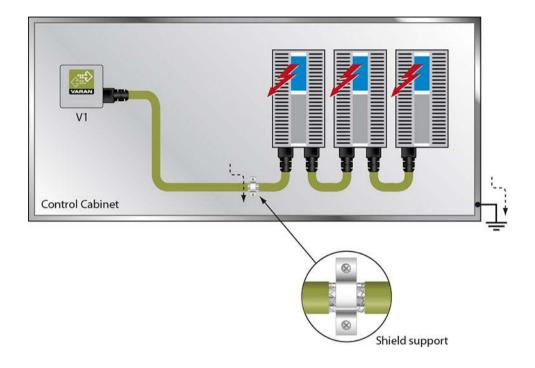

## 4. Connecting Noise-Generating Components

With the connection of power components that generate strong electromagnetic noise, it is also critical to ensure correct shielding. The shielding should be placed before a power component (or a group thereof).

## 5. Shielding Between Two Control Cabinets

If two control cabinets must be connected over a VARAN bus, it is recommended that the shielding be located at the entry points to both cabinets. Noise can thereby be kept from reaching the electronics within the control cabinet.